AperTO - Archivio Istituzionale Open Access dell'Università di Torino

## A 64-channel waveform sampling ASIC for SiPM in space-born applications

| This is a pre print version of the following article:                                                                                                                                                                                                                                                                                                                 |                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Original Citation:                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                       |                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                       |                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                       |                            |  |  |  |

| Availability:                                                                                                                                                                                                                                                                                                                                                         |                            |  |  |  |

| This version is available http://hdl.handle.net/2318/1946726                                                                                                                                                                                                                                                                                                          | since 2023-12-08T10:08:44Z |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                       |                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                       |                            |  |  |  |

| Published version:                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |

| DOI:10.1088/1748-0221/18/02/C02022                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |

| Terms of use:                                                                                                                                                                                                                                                                                                                                                         |                            |  |  |  |

| Open Access                                                                                                                                                                                                                                                                                                                                                           |                            |  |  |  |

| Anyone can freely access the full text of works made available as "Open Access". Works made available<br>under a Creative Commons license can be used according to the terms and conditions of said license. Use<br>of all other works requires consent of the right holder (author or publisher) if not exempted from copyright<br>protection by the applicable law. |                            |  |  |  |

(Article begins on next page)

- 1 PREPARED FOR SUBMISSION TO JINST

- 2 TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS TWEPP 2022

- 3 19-23 SEPTEMBER 2022

- 4 BERGEN NORWAY

# **A 64-channel waveform sampling ASIC for SiPM in**

space-born applications

# <sup>7</sup> S. Tedesco,<sup>a,1</sup> A. Di Salvo,<sup>b</sup> A. Rivetti<sup>b</sup> and M. Bertaina<sup>c</sup>

<sup>8</sup> <sup>a</sup> Politecnico di Torino, Corso Duca degli Abruzzi, 24, Torino, Italy

<sup>9</sup> <sup>b</sup>INFN sezione di Torino, via Pietro Giuria 1, Torino, Italy

<sup>10</sup> <sup>c</sup>Università degli Studi di Torino, via Pietro Giuria 1, Torino, Italy

11 E-mail: silvia\_tedesco@polito.it

12 ABSTRACT: The architecture of a 64-channel ASIC for the readout of Silicon Photomultipliers in

13 space experiments is described. Each channel embeds a front-end amplifier with a common gate

topology followed by a 256 cells analogue memory with a sampling frequency of 200 MHz. A

15 single memory cell includes a storage capacitor, a single-slope Analog-to-Digital Converter (ADC)

- <sup>16</sup> with programmable resolution between 7 and 12 bits and the digital control logic. To save power,

- 17 the A/D conversion is carried-out only when a trigger signal is received. The trigger can either be

- <sup>18</sup> generated inside the ASIC or provided by an external source. The analogue samples are digitized in

- <sup>19</sup> parallel, thus reducing the conversion dead time. The memory cells can be arranged in a single array

- <sup>20</sup> or they can be grouped in shorter slots of 32 or 64 cells that work in a multi-buffer configuration.

- <sup>21</sup> The channels can work independently or they can be synchronised to acquire the same time-frame

- <sup>22</sup> in the full chip. The target power consumption is 5 mW/channel. The ASIC is being designed in a

- <sup>23</sup> 65-nm CMOS technology. A digital-on-top flow is applied for the integration and final validation

- of the chip. The tape-out is scheduled in the first quarter of 2023.

<sup>25</sup> KEYWORDS: VLSI circuits, Front-end electronics for detector readout

<sup>&</sup>lt;sup>1</sup>Corresponding author.

#### 26 Contents

| 27 | 1 | Introduction      | 1 |

|----|---|-------------------|---|

| 28 | 2 | ASIC architecture | 1 |

| 29 |   | 2.1 Front-End     | 2 |

| 30 |   | 2.2 Analog Memory | 2 |

| 31 | 3 | Conclusions       | 5 |

#### 32 1 Introduction

Silicon Photomultipliers (SiPMs) are today employed in many different fields such as High Energy 33 Physics (HEP) instrumentation [1], LIDAR [2], Positron Emission Tomography (PET)[3]. Due to 34 their good detection efficiency, compactness and capability to work with moderate power supply 35 voltages they are becoming more and more attractive also for space-born applications. SiPM are 36 considered, for instance, to equip on board cameras of future satellite-based cosmic ray observato-37 ries. In this context, they will be used to detect the Cherenkov light produced by the interaction of 38 Ultra-High Energy Cosmic Rays (UHECRs) and neutrinos with the terrestrial atmosphere [5]. 39 Two common approaches to readout SiPMs rely on charge integration [6] or photon counting 40 technique [7]. However, these solutions do not allow to study in detail the signal waveform and, 41 as a consequence, to distinguish the signal of interest from spurious signals created by the direct 42 interaction of cosmic rays within the sensor. For the method to be effective, the waveform should 43 be captured with a sampling frequency of at least 100 Ms/s. A large dynamic range (up to 12 bits) 44 is also required as the energy of the primary particle can span several orders of magnitudes. High 45 integration density is desired to keep the overall system compact and lightweight and low power 46 dissipation is mandatory. Therefore, a single channel should offer a complete signal processing 47 chain with a power budget of only a few milliwatts. Care must be paid to radiation tolerance as 48 well, with particular emphasis on Single Event Effects. On the basis of these considerations, the 49 design of a custom ASIC optimized to read-out a SiPM-based Cherenkov radiation imager has been 50 undertaken. The key target specifications are a sampling frequency of 200 Ms/s, a maximum power 51 consumption of 5 mW/channel and a dynamic range of 12 bits. 52

#### 53 2 ASIC architecture

The 64-channel ASIC is being designed in a commercial 65-nm CMOS technology and must operate with a power supply of 1.2 V. The choice of the technology stems from the fact that it provides a good integration density and its radiation tolerance has been extensively studied. The straightforward approach in a waveform sampling system, is having one free running ADC per channel followed by a digital signal processor. Despite the impressive progress made in ADC developments [8], [9], the <sup>59</sup> use of one 12-bit ADC per channel would hardly be compatible with the target power consumption.

<sup>60</sup> Furthermore, since the flux of UHECRs is extremely low (0.1 to 100 particles per hour are expected

[10]), a continuous digitization is unnecessary. Analog memories provide instead an interesting

<sup>62</sup> alternative to capture fast transient signals occurring sparsely in time.

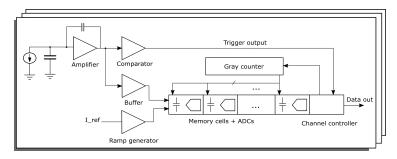

The block diagram of one channel is shown in figure 1. The current pulse coming from the sensor is amplified and converted into a voltage by the input amplifier. The resulting voltage is buffered into a 256-cells analog memory which is used to store temporarily the signal information.

Figure 1: Channel block diagram.

When the sampling is enabled, the cells are written with a frequency of 200 MHz and the 66 memory works as a ring buffer. If an event occurs, a trigger signal is issued and the cells enter the 67 digitization phase, otherwise they are overwritten. In order to perform background monitoring, an 68 external trigger can be sent to the chip. The analog memory can work as a single buffer or it can 69 be divided into a maximum of 8 segments of 32 cells each thus enabling multi-buffering mode. By 70 segmenting the analog memory, the data are derandomized, so the system can acquire an event even 71 if the processing of the previous one is still in progress. Furthermore, the channels of the ASIC can 72 be programmed to operate in parallel (imaging mode) or independently from each others (sparse 73 mode). The digitized data are transmitted off-chip by employing a 8-channel Double Data Rate 74 (DDR) serializer operating with a frequency of 400 MHz. 75

## 76 2.1 Front-End

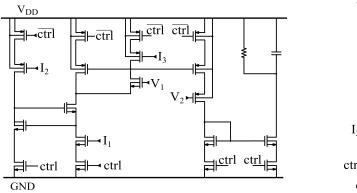

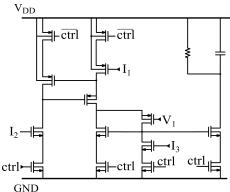

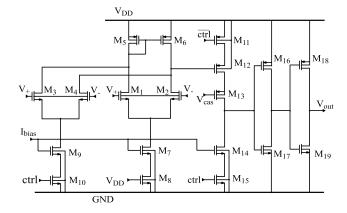

The front-end amplifier is based on the common gate topology [11]. Both polarities of the amplifier 77 have been implemented to read positive and negative pulses thus increasing the flexibility of the 78 chip. The two schematics are shown in figures 2a and 2b. This stage includes also a comparator 79 to provide a local trigger. In sparse mode, each channel is triggered independently. In imaging 80 mode, two trigger modalities are foreseen: a fast or between the channels and a topological trigger 81 that looks at the firing on nearby channels. The generated information can either be used to trigger 82 a readout sequence directly on the chip or it can be provided as primitive to an external trigger 83 processor, that looks at the trigger outputs of different ASICs before issuing a final trigger decision. 84

## **85** 2.2 Analog Memory

The basic building blocks of the analogue memory is the sampling cell. Several options can be considered to digitize the sampled data. One possibility is to have a fast ADC per channel or per group of channels. However, even using a moderate speed ADC (e.g. 20 Ms/s), 12.8  $\mu$ s are

(a) Front-end amplifier with NMOS input.

(b) Front-end amplifier with PMOS input.

needed to readout 256 cells. The Wilkinson ADC topology is attractive for its simplicity, but it has 89 long conversion time. However, it requires a limited number of hardware resources. Therefore, a 90 massive parallelism can be used to keep the overall conversion time of the memory to an acceptable 91 level. For instance, in [12] a fast sampling ASIC with an analog memory of 128 cells is described. 92 The digitization is fulfilled by using 128 10-bit single-slope ADCs placed at the periphery of the 93 chip. Therefore, all the cells in a single channel are converted in parallel. However, the scaling 94 in CMOS technologies allows to develop chip with even higher integration density. Hence, in our 95 device a 12-bit single-slope ADC has been embedded direcly in each memory cell. This allows to 96 digitize all the samples in the ASIC in parallel thus reducing the dead time. The time needed for 97 the conversion is given: 98

$$2^N \times T_{clk} = 20.48 \,\mu m$$

(2.1)

where N is the resolution and  $T_{clk}$  represents the clock period of 5 ns. The resolution of 99 the converter can be programmed between 8 and 12 bits. Hence, with a lower resolution, this 100 time interval is decreased. For instance, for a 10-bit resolution (that could still adequate for our 101 purpose) the conversion shrinks to  $5.12 \,\mu s$ . However, in a waveform sampling ASIC an important 102 contribution to dead time is also given by data transmission. In fact, the digital data stream is 103 composed of a 27-bit long header and the digitized data. By selecting the maximum resolution 104 for the ADC, an amount of 3099 bits per channel must be transmitted to readout 256 cells. Even 105 using 10 Gbit/s serializer per chip the time to send the raw data out would be 19.83  $\mu$ s. Data could 106 be of course zero-suppressed and compressed on chip before transmission. However, it has been 107 preferred to defer a more elaborated signal processing to the on-board FPGA. To increase the system 108 modularity and thus its fault tolerance, instead of using a single, fast serializer 8 DDR serializers 109 working with a 400 MHz clock have been implemented. This allows to segment the ASIC in 110 modules of 8 channels which are basically independent of each other. The data transmission time 111 thus becomes  $30.99 \,\mu s$  in the worst case in which all the 256 cells are used to capture a single event. 112 The building blocks of the memory cell are shown in figure 3a. Each cell includes the sampling 113 capacitor, the comparator of the ADC, some switches and a control logic (not illustrated in the 114 figure). A single Gray counter whose outputs are shared among the ADCs, is embedded in each 115

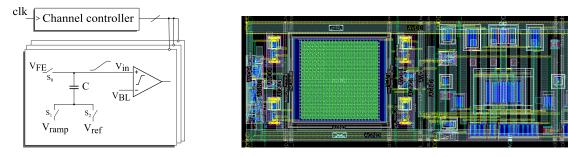

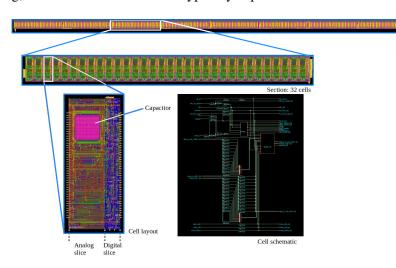

(a) Memory cell building blocks.

(b) Layout of the memory cell.

channel. In the sampling phase, the storage capacitor is charged to a voltage equal to  $V_{FE} - V_{ref}$ , 116 where  $V_{FE}$  is the output of the input amplifier and  $V_{ref}$  is a reference voltage. In contrast with the 117 most common architecture [13], the minus terminal of the comparator is not connected to a ramp 118 generator. In fact, this solution can deteriorate the linearity of the system because the common mode 119 of the comparators changes between the cells. A possibile solution consists in fixing the threshold 120 to a steady value while charging the capacitor through a constant current generator. However, the 121 mismatch between the current sources can lead to gain variation between the cells. Hence, a single 122 ramp generator is applied to all the storage capacitor. During the digitization the top plate of the 123 capacitor is connected only to a gate terminal of a MOS transistor, so this node remains floating. 124 Hence, if a ramp generator is connected to the bottom plate, the same voltage variation is replicated 125 on the top thanks to charge conservation. When the voltage on this terminal reaches the threshold, 126 the comparator flips triggering the storage into local latches of the output of the Gray counter. This 127 allows to embed a single ramp generator which is common to all the cells in a single channel as 128 shown in ref. [13], but this alternative approach ensures good gain uniformity between the cells. 129

Figure 4: Comparator schematic.

The schematic of the comparator is shown in figure 4. It has two possible states which are called power-up and power-down mode. In power-up mode, a bias current of  $2 \mu A$  is provided to this block. On the other hand, when the digitization is disabled, the current is reduced by three quarter in order to reduce the power wasting when the comparator is not operating. However, this <sup>134</sup> block is not completely switched off thus allowing a fast warm-up. Hence, before digitization, 1-2

<sup>135</sup> clock cycles are dedicated to power up of the converters and to switch the bottom plates of the

<sup>136</sup> capacitors from the fixed reference to the voltage ramp.

The final layout of the cell has a size of  $43.62 \times 15.20 \,\mu m^2$  and it is illustrated in figure 3b. 137 This sizing allows to integrate the analog memory in a chip with final dimensions of  $6mm \times 4mm$ . 138 The analog cell is integrated with a digital-on-top methodology. Figure 5 reports a preliminary 139 layout where the Wilkinson ADC is included alongside the latches. The upper part of the image 140 depicts the layout of block named section in which the cells are hierarchically organized and the 141 ensemble of the eight sections. Each section is managed by a digital channel controller (not shown 142 in the layout) where dedicated Finite State Machines (FSMs) are implemented. These FSMs take 143 into account the partitioning of cell array by appropriately managing the sampling, digitizing and 144 readout states. The channel controller also drives the configurable Gray counter whose output is 145 distributed to each section. A first estimate of the digital power was evaluated by synthesizing each 146 block and the consumption is limited to 1.3 mW per channel. Since this value does not consider 147 the final routing, a variation around 30 % is typically expected. 148

Figure 5: Layout of a section

#### 149 3 Conclusions

This paper presented the architecture of a 64-channel ASIC for SiPM readout in space environment. 150 The input current pulse is amplified, converted into a voltage value and stored into a 256-cells analog 151 memory. The memory cells allow to acquire a snapshot of the incoming event with a resolution 152 of 12 bits. Sampling and digitization steps are decoupled since the conversion starts only if a 153 trigger signal (both generated internally or provided from the outside) is received. This allows to 154 obtain lower power consumption compared to the implementation of a free-running converter. The 155 chip flexibility has been increased by applying the derandomization technique. The ASIC is being 156 designed in a commercial 65-nm CMOS technology. The power consumption aims to be 5 mW/ch 157 considering both analog and digital circuits. The integration of the building blocks is ongoing and 158 the chip tape-out is scheduled at the beginning of 2023. 159

#### 160 **References**

- [1] F. Sefkow, *The CALICE tile hadron calorimeter prototype with SiPM read-out: Design, construction and first test beam results, 2007 NSSCR* vol. 1 (2007) pg. 259-263.

- [2] A. M. Antonova, V. A. Kaplin, *SiPM timing characteristics under conditions of a large background for lidars, Journal of Physics: Conference Series* vol. 945 (2007) pg. 012012.

- [3] M.G. Bisogni, M. Morrocchi, Development of analog solid-state photo-detectors for positron

emission tomography, Nuclear Instruments and Methods in Physics Research Section A: Accelerators,

Spectrometers, Detectors and Associated Equipment vol. 809 (2016), pg. 140-148.

- [4] M.G. Bagliesi, et al., A custom front-end ASIC for the readout and timing of 64 SiPM photosensors,

Nuclear Physics B-Proceedings Supplements 215.1 (2011), pg. 344-348.

- [5] A.V. Olinto, J. Krizmanic, *The Roadmap to the POEMMA Mission, APS April Meeting Abstracts*,

(2021), pg. D21-006.

- [6] L. Buonanno et al., *GAMMA: a 16-channel spectroscopic ASIC for SiPMs readout with 84-dB* dynamic range, IEEE Transactions on Nuclear Science (2021), 2556-2572.

- [7] S. P. Nambboodiri et al., A Current-Mode Photon Counting Circuit for LongRange LiDAR

Applications, 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS)

(2020), pg. 146-149.

- [8] H. Liu et al., A 12-bit 200MS/s Pipelined-SAR ADC in 65-nm CMOS with 61.9 dB SNDR, 2019 IEEE

International Conference on Electron Devices and Solid-State Circuits (EDSSC) (2019), pg. 1-2.

- [9] L. Ricci, L. Bertulessi, A. Bonfanti, A low-noise high-speed comparator for a 12-bit 200-MSps SAR

ADC in a 28-nm CMOS process, SMACD/PRIME 2021; International Conference on SMACD and

16th Conference on PRIME (2021), pg. 1-4.

- [10] A.L. Cummings et al., Detection of the above the limb cosmic rays in the optical Cherenkov regime

using sub-orbital and orbital instruments, 37th Intern. Cosmic Ray Conf.(2021), 437 PoS(ICRC2021)437.

- [11] P. Carniti et al, *CLARO-CMOS*, a very low power ASIC for fast photon counting with pixellated photodetectors, Journal of Instrumentation 7.11 (2012), pg. 11026.

- [12] S. Kleinfelder, A multi-GHz, multi-channel transient waveform digitization integrated circuit, 2002

*IEEE nuclear science symposium conference record* vol. 1 (2002), pg. 544-548.

- [13] E. Delagnes et al, A Low Power Multi-Channel Single Ramp ADC With up to 3.2 GHz Virtual Clock,

*IEEE Transactions on Nuclear Science* vol. 54 (2007), pg. 1735-1742.